Spectrum Analyzer

32 kHz bandwidth 24 bits ADC , so noise floor at about 120 dB Interfacing with PC Single channel White noise generator Can make Bode plot

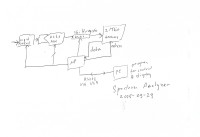

I intend to make a spectrum analyzer to analyze low distortion audio systems. I want to use a 24 bit ADC at 64 kHz.It will operate at a clock of 1024 kHz, so with an oversampling rate of 16 times.

When the ADC has taken a sample (15.625 us between samples) there are about 15 us available to read the data in serial format. The data can be clocked out by the SCLK- signal (Serial Clock) of at least 1.6 MHz. This can be done by at 64 MHz uP. A 24 bit shift register will be used to catche the sample. When 64 k samples are taken, the data will be transported to the PC. There the FFT wil be executed and the gathered data can be displayed.

Intended specifications:

Sampling rate 64 KHz

Noise floor about -120dB

Maximum input 5 V or 50 V peak. (internal attanuator)

Horizontal resolution 1, 2 or 4 Hz. (selectable)

Time for displaying one sample with high resolution:

taking sample: 1 s.

Transport: 12 s.

Making FFT:

Power dissipation: Expected < 2 W

Costs: Components < € 50

PCB € 100

Case < € 20

Needed time to complete project: 1 year

2025-10-17

Added: first circuit diagrams, preliminary.

2025-10-22

Some elucidation at the circuit diagram.The used ADC is the AD7767-1. The signal is coming in at X101 at the left of the "Front End". There are two attenuation stages for 5x and 2x attenuation (14 and 6 dB). The input circuit can handle + / - 5 V. The maximum input at X101 is + / - 50 V, 35 Vrms. When the input is too high the output of IC103 comes out of the range of Vref and will switch off the reed relais for maximum attenuation.

On the page "Digital" we see the uP PIC18F44K22. The memory is not important but I need a lot of outputs to control the ADC and the memory. At he low side of the page there is the shift register with IC202, 205 and 208. They are accompanied by latches IC220, 206, 209. IC207 is a 2-Mbit memory. IC204 and 210 form an 18 bit adrescounter for the memory. The uP, latches and the memory share an 8-bit data bus. To prevent ground loops isolator IC212 is added. IC215 translates RS232 to an USB -signal.

I have added a "Noise Generator" in order to ease measurements at audio equipment. It consists of a 16-bit shift register, sot it generates a sequence of maximum 2^16 - 1. IC306, 307 and 310 detect when there all ones in the register and can trigger the start of the AD-conversion. This makes comparison of audio circuits possible and an BODE-plot can easily be calculated.

2025-11-18

When the ADC has taken a sample (15.625 us between samples) there are about 15 us available to read the data in serial format. The data can be clocked out by the SCLK- signal (Serial Clock) of at least 1.6 MHz. This can be done by at 64 MHz uP. A 24 bit shift register will be used to catche the sample. When 64 k samples are taken, the data will be transported to the PC. There the FFT wil be executed and the gathered data can be displayed.

Intended specifications:

Sampling rate 64 KHz

Noise floor about -120dB

Maximum input 5 V or 50 V peak. (internal attanuator)

Horizontal resolution 1, 2 or 4 Hz. (selectable)

Time for displaying one sample with high resolution:

taking sample: 1 s.

Transport: 12 s.

Making FFT:

Power dissipation: Expected < 2 W

Costs: Components < € 50

PCB € 100

Case < € 20

Needed time to complete project: 1 year

2025-10-17

Added: first circuit diagrams, preliminary.

2025-10-22

Some elucidation at the circuit diagram.The used ADC is the AD7767-1. The signal is coming in at X101 at the left of the "Front End". There are two attenuation stages for 5x and 2x attenuation (14 and 6 dB). The input circuit can handle + / - 5 V. The maximum input at X101 is + / - 50 V, 35 Vrms. When the input is too high the output of IC103 comes out of the range of Vref and will switch off the reed relais for maximum attenuation.

On the page "Digital" we see the uP PIC18F44K22. The memory is not important but I need a lot of outputs to control the ADC and the memory. At he low side of the page there is the shift register with IC202, 205 and 208. They are accompanied by latches IC220, 206, 209. IC207 is a 2-Mbit memory. IC204 and 210 form an 18 bit adrescounter for the memory. The uP, latches and the memory share an 8-bit data bus. To prevent ground loops isolator IC212 is added. IC215 translates RS232 to an USB -signal.

I have added a "Noise Generator" in order to ease measurements at audio equipment. It consists of a 16-bit shift register, sot it generates a sequence of maximum 2^16 - 1. IC306, 307 and 310 detect when there all ones in the register and can trigger the start of the AD-conversion. This makes comparison of audio circuits possible and an BODE-plot can easily be calculated.

2025-11-18

The planned 74HC594 are replaced by 74HC595 for the shift tegister. They have a latch and a tristate output, this eliminates the need for the 74HC573.

Counters 74HC112 are replaced by 74HC73.

2026 -04-10

The first sample is up and operating. See the added circuit diagram and the premininary result. Still a lot of software work has to be done. Will be continued.

2026 -04-10

The first sample is up and operating. See the added circuit diagram and the premininary result. Still a lot of software work has to be done. Will be continued.

Discussion (1 commentaire(s))