Carte d'évaluation FPGA GateMate

4 novembre 2022

sur

sur

La famille de FPGA GateMateTM de Cologne Chip AG répond à toutes les exigences d'application des FPGA de petite et moyenne taille. La capacité logique, la consommation d'énergie, la taille du boîtier et la compatibilité avec les circuits imprimés sont les meilleures de leur catégorie. Ils combinent ces caractéristiques avec le coût le plus bas de l'industrie, ce qui rend les dispositifs bien adaptés aux projets universitaires et aux applications de grand public.

Afin d'offrir la plus large gamme possible d'applications pour votre évaluation, la carte d'évaluation offre tous les composants périphériques minimums requis tels que la mémoire, l'horloge et l'accès à un grand nombre d'interfaces et permet de contrôler les tensions du noyau et des E/S.

Caractéristiques de la carte GateMate

Plus d'informations >>>

Traduction : Maxime Valens

Prête à l'emploi

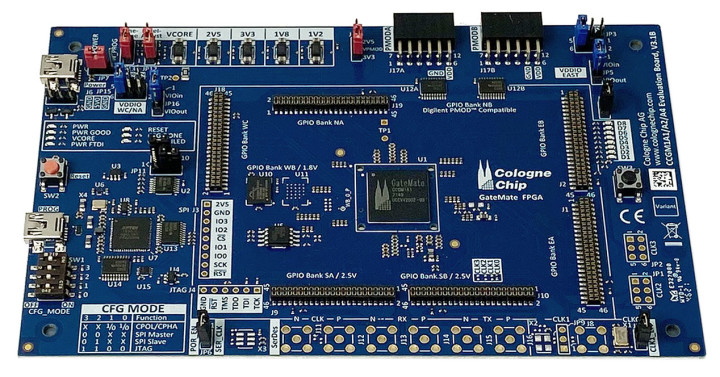

La carte d'évaluation GateMateTM est une plateforme de développement prête à l'emploi et riche en fonctionnalités pour le FPGA CCGM1A1 de Cologne Chip. Elle sert de conception de référence et permet d'entrer directement dans le développement d'applications qui peuvent être adaptées à chacune des six banques d'E/S disponibles. La fixation de matériel supplémentaire est un jeu d'enfant grâce aux connecteurs Pmod : ils permettent d'accéder à une variété de cartes périphériques, y compris des contrôleurs de moteur, des capteurs, des écrans et plus encore.Afin d'offrir la plus large gamme possible d'applications pour votre évaluation, la carte d'évaluation offre tous les composants périphériques minimums requis tels que la mémoire, l'horloge et l'accès à un grand nombre d'interfaces et permet de contrôler les tensions du noyau et des E/S.

Caractéristiques de la carte GateMate

- FPGA GateMate A1

- 20 480 éléments programmables

- Tension du cœur de 0,9-1,1 V, tension E/S de 1,2-2,5 V

- 32 cellules de mémoire vive à double port, total : 1 280 Kbit

- 4 PPL configurables

- Tous les E/S configurables en paires asymétriques ou différentielles LVDS

- Boîtier BGA à 324 billes au pas de 0,8 mm, dimensions 15 x 15 mm

- Interfaces

- Interface de configuration USB-JTAG + USB-SPI

- 2 ports compatibles Pmod

- 6 banques GPIO

- Mémoire

- Flash SPI Quad-I/O 64 Mbit

- HyperRAM 64 Mbit

- Dimensions

- 100x160 mm (standard Eurocard)

Plus d'informations >>>

Traduction : Maxime Valens

Lire l'article complet

Hide full article

Discussion (0 commentaire(s))