Nouvelle carte CPLD : davantage de logique avec la famille MAX10

4 mai 2019

sur

sur

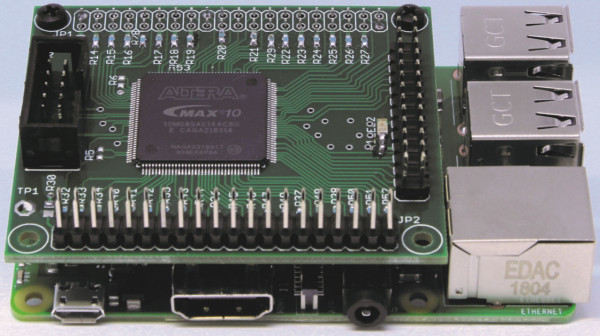

Dans le numéro de mai-juin 2018 d'Elektor, l'auteur a proposé une carte équipée d'une puce CPLD de la famille MAX-II d'Altera (aujourd'hui Intel). La puce utilisée dans ce projet, une EPM570, est une CPLD avec 570 éléments logiques dans un boîtier TQFP100 (Thin Quad Flat Pack à 100 pattes). La carte acceptait aussi des puces EPM240, plus petites mais avec un brochage compatible. Du fait de la taille relativement petite du boîtier, il était possible de concevoir une carte de prototypage de telle sorte que la puce était pratiquement utilisable comme un circuit DIL.

Avec 570 éléments logiques, on peut déjà réaliser une bonne quantité d'applications, mais s'ils ne suffisent pas, il faut se tourner vers une autre famille de CPLD. Comme la famille MAX-V n'offre que peu d'avantages par rapport à la famille MAX-II, pourquoi ne pas passer directement à la famille la plus récente d'Intel, la MAX10 ? Cette famille est composée de sept groupes de produits CPLD, chacun avec des variantes diverses. On a le choix : de 2.000 à 50.000 éléments logiques, alimentation à tension simple ou double, avec régulateur 3,3 V intégré (auquel cas, le modèle est obligatoirement mono-tension), différentes tailles de pages de mémoire flash, des convertisseurs A/N, un capteur de température, flash à double configuration (deux images dynamiques utilisables sur la même puce) et bien d'autres fonctions.

De la CPLD à la FPGA

Au-delà des pures fonctions CPLD, la famille MAX10 possède des fonctions FPGA totalement opérationnelles, telles que des PLL internes (jusqu’à 4) pour produire des signaux d'horloge plus rapides, des processeurs programmables NIOS, des blocs de traitement numérique du signal et des pilotes de mémoires DDR3.Toutes ces variantes sont disponibles dans des boîtiers variés (de la galette de semi-conducteur (wafer) aux gros boîtiers avec des centaines de broches d’E/S). Voilà d'ailleurs notre premier critère de choix. Le seul boîtier encore soudable par l'amateur (c'est-à-dire avec un fer à souder) est un EQFP de 144 pattes. Avec ses 22×22 mm2, ce modèle nécessite un circuit imprimé un peu plus grand que son prédécesseur, mais offre en échange 101 entrées-sorties utilisables (pour toutes les variantes). Pour plus de détails, consulter le manuel utilisateur de la famille MAX10.

Composants à ajouter

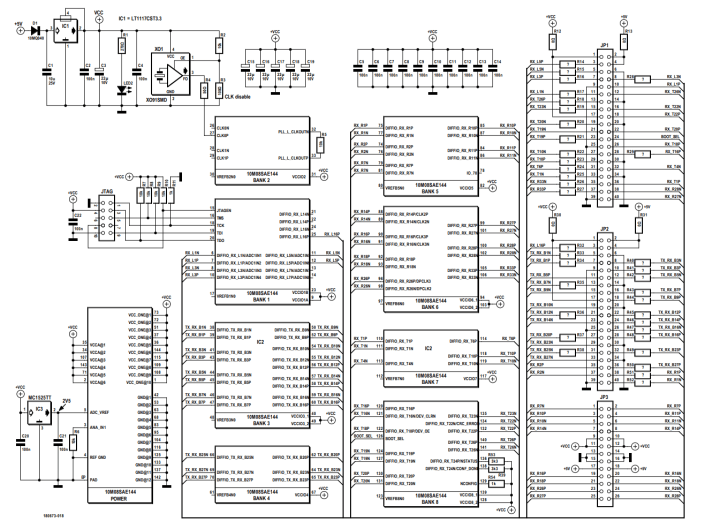

La figure 1 montre le schéma de la carte pour cette nouvelle puce CPLD plus « grosse » en taille et en fonctions. On y distingue un régulateur de tension avec ses condensateurs de filtrage, une horloge et le connecteur JTAG pour la programmation. On y trouve encore une référence de tension pour le convertisseur A/N intégré à la CPLD (bank 1A).

Le prototype est équipé d'une puce 10M08 qui possède huit unités logiques (LE), une PLL et un convertisseur A/N. La carte est compatible avec toutes les puces de la famille MAX10 de 2.000 à 50.000 éléments logiques, dans la mesure où elles sont logées dans un boîtier EQFP-144. La conception du circuit imprimé s'appuie sur quatre couches pour garantir un fonctionnement sûr, même aux fréquences d'horloge les plus élevées.

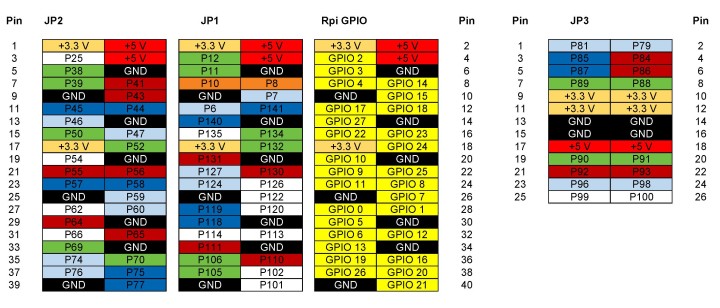

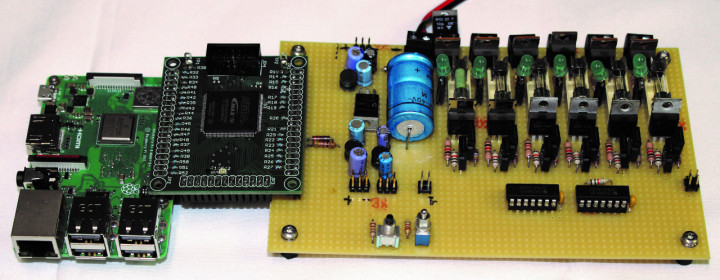

Comme avec la précédente carte, il y a une bonne raison de ne pas router vers les connecteurs d'accès toutes les entrées/sorties possibles. La carte peut être utilisée comme une grosse puce DIL installée sur une platine d'essai ou une carte à trous, mais elle possède un raffinement : le brochage des deux connecteurs latéraux est calqué sur celui du connecteur GPIO à 2×20 broches du Raspberry Pi (à partir de la version 2). On peut donc les enficher directement sur le RPi, ce qui permet de combiner la puissance de calcul et l'interface du RPi avec les possibilités matérielles d'une puce CPLD moderne. La figure 2 présente l'affectation des broches des trois connecteurs d'accès (avec les broches de la puce CPLD) comparée au connecteur GPIO du RPi. Les broches représentées côte à côte avec la même couleur forment une paire d'entrées ou de sorties différentielles qui peuvent bien entendu être aussi utilisées isolément, comme les broches sans couleur.

Variantes

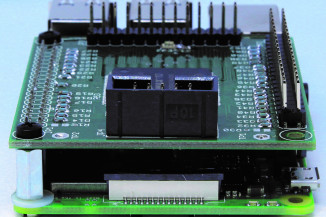

Les trous de fixation sont alignés.

La figure 4 montre comment le RPi pilote la puce CPLD via le connecteur JP2, laquelle gère un circuit électronique (par ex. un étage de puissance) sur carte à trous. On peut alimenter les deux cartes en commun ou séparément, c’est configurable avec les ponts (résistances de 0 Ω) R12, R13, R30 et R31.

Premier arrivé, premier servi

Quelques circuits imprimés vierges ou partiellement équipés (de la puce CPLD seulement) sont disponibles chez l’auteur alfred_rosenkraenzer@gmx.de. N’hésitez pas à en demander un.@www.elektor.fr

Carte de liaison CPLD au format DIL avec CMS monté (MAX-II), K1 à K4 fournis (projet du numéro 5-6/2018)

www.elektor.fr/cpld-bob

(180673)

➔ Intéressé(e) par la lecture d'autres articles du magazine Elektor ? Devenez membre dès maintenant !

Lire l'article complet

Hide full article

Discussion (0 commentaire(s))