Développement du Parallax Propeller 2 : un entretien avec Chip et Ken Gracey

sur

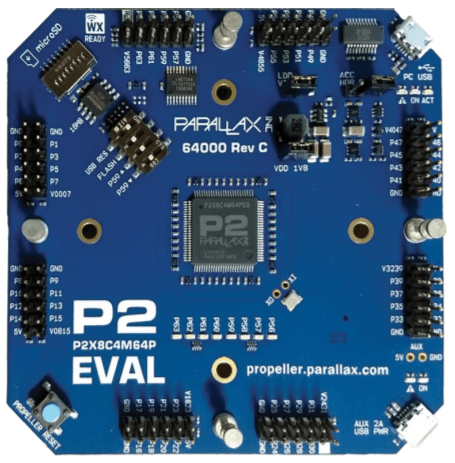

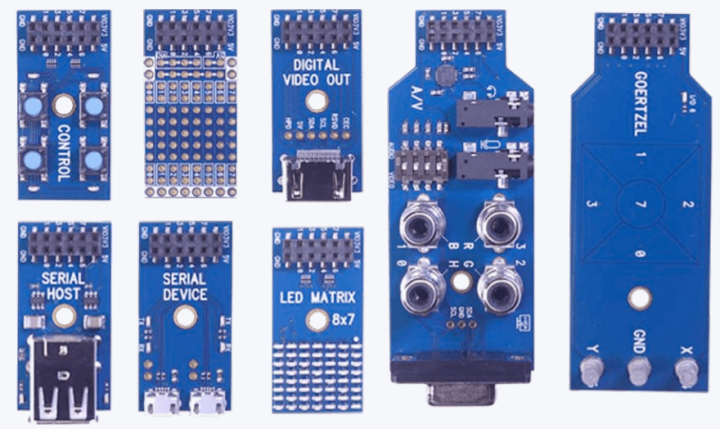

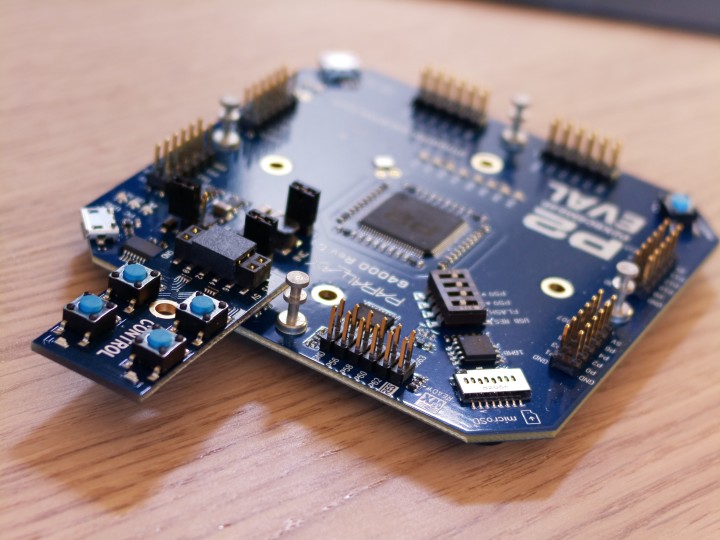

Sorti il y a près de 16 ans, le Propeller 1 de Parallax proposait huit cœurs dans un petit boîtier DIP-40 ou QFP avec une fréquence d'horloge pouvant atteindre 80 MHz sur tous les cœurs. En novembre 2020, la société basée à Rocklin, en Californie, a officiellement lancé le Propeller 2, un microcontrôleur à huit cœurs fonctionnant jusqu'à 300 MHz avec plus de RAM, des broches supplémentaires et de nouveaux périphériques. Consultez la série d'articles en cinq parties de Mathias Claussens, Propeller 2 de Parallax, pour plus de détails. Le Propeller 2 est unique à bien des égards, c'est pourquoi nous avons profité de l'occasion pour parler avec le fondateur de Parallax, Chip Gracey, et son frère, Ken Gracey, de la puce et de son développement.

Les leçons apprises

Elektor : Le Propeller 2 est maintenant disponible. Quelles leçons avez-vous tirées du Propeller 1, et comment les avez-vous appliquées second ?

Chip : Pour le Propeller 1, nous avions huit cœurs, appelés cogs. La limite était que si nous avions beaucoup de tâches à bande passante très élevée qui nécessitaient une interaction intensive avec le CPU, tous les cogs pouvaient parfois être épuisés assez rapidement. Sur le Propeller 2, les broches d'E/S sont dotées d'un grand nombre de fonctions intelligentes, de sorte que chacune dispose de trois registres de 32 bits, ce qui nous permet de la configurer pour toutes sortes de modes de mesure et de communication différents. Ces broches gèrent l'interaction à bande passante très élevée et le processeur est déchargé. Nous avons ajouté de nombreuses fonctions analogiques aux broches d'E/S, de sorte que chacune comporte trois CNA différents, dont deux à relativement faible impédance, qui peuvent émettre des signaux analogiques très rapidement. Nous avons également intégré des convertisseurs analogiques-numériques (CAN) à chaque broche ; il s'agit de convertisseurs delta-sigma. Mais dans les broches smarts, par exemple, nous faisons également un filtrage par sommation.

Elektor : La conception du Propeller 2 était-elle similaire à celle du Propeller 1, une conception de CPU à partir de zéro en termes d'architecture ?

Chip : Je pense que sur le Propeller 1 original, nous avions peut-être 63 instructions. Nous en avons beaucoup plus sur le Propeller 2. Environ 350. Elles font diverses choses spécifiques, mais elles sont aussi un peu comme des blocs de construction.

Elektor : Concevoir un nouveau CPU à partir de rien : combien de temps s'est-il écoulé entre les premières lignes sur papier et la puce finale ?

Chip : Jusqu'à ce que le Propeller 2 soit terminé, il a fallu 14 ans, ce qui, sur le marché, est tout à fait déraisonnable. Le monde connaît quelques changements importants en matière de technologie dans ce laps de temps. Mais ce que nous avons fait pour cette puce, c'est que nous nous sommes vraiment concentrés sur un grand nombre de questions de principe, qui ne seront jamais dépassées.

Ken : Je tiens à souligner qu'au cours de cette période de 14 ans, Chip a appris énormément de choses, et nous avons dû recommencer avec de nouvelles conceptions au fur et à mesure qu'il apprenait, en faisant plusieurs séries de fonderie de pièces, ou de la puce entière. C'était un processus d'apprentissage qui demandait beaucoup de patience.

Chip : Nous avons commencé à penser en termes de schémas. Mais c'est vraiment inefficace quand on a affaire à des choses comme des bus à 32 bits. Vous ne voulez pas écrire des schémas pour tous ces fils. C'est ainsi que Le Propeller 1 a été conçu. Le second est abstrait et écrit en Verilog.

Elektor : Parlons de la construction de périphériques. Quels étaient ceux les plus difficiles à construire pour la puce ?

Chip : Vous avez mentionné les broches smarts. La chose la plus difficile les concernant était le mode USB, parce que c’est un protocole très arbitraire. Ils auraient pu faire en sorte qu’il soit implémentable en logiciel sur des CPU rapides, mais ils l'ont conçu de telle sorte qu'il y a certains timing très serrés où les contrôles CRC doivent être effectués. Cela signifie que vous devez réaliser une implémentation en silicium pour réaliser l'USB. C’est un système compliqué qui nécessite beaucoup de connaissances spécialisées pour fonctionner et qui est difficile à valider.

Elektor : Pour mettre le design en silicium réel, comment avez-vous choisi votre fabricant ?

Chip : Nous avons un peu tourné autour du pot. Pendant un certain temps, nous avons opté pour le modèle de la fonderie pure, où nous fournissions le jeu de masques complet pour notre conception, puis une fonderie fabriquait la puce. Nous avons testé des puces de cette manière, mais pas des puces complètes. Le Propeller 2, je crois, contient environ 630 000 instances de cellules standard qui constituent la logique qui contrôle tout. Nous n'avons pas assez de temps dans nos vies pour trouver comment concevoir tout cela de manière optimale à partir de notre code Verilog. Mais nous n'avons pas non plus la capacité d'optimiser suffisamment pour que le timing soit respecté. Le processus 180 nanomètres utilisé est sorti depuis, je crois, en 1999. Avec de si bons outils, des outils de synthèse et des bibliothèques de cellules standard, il est étonnant que notre puce puisse être cadencée jusqu'à 350 MHz. Nous pensions que 180 MHz serait la limite pratique. À haute température, à faible tension d'alimentation, dans les pires conditions de traitement, 180 MHz est la limite inférieure garantie. Mais il est étonnant de voir à quel point les outils d'optimisation d'aujourd'hui sont performants, de sorte qu'il est possible de revenir à des technologies de silicium plus anciennes et d'en tirer des performances bien supérieures.

Pourquoi sommes-nous allés chez Onsemi ? Nous sommes un peu comme un mendiant qui ne choisit pas, car nous sommes une petite entreprise et nos ressources sont limitées. Je ne sais pas comment nous sommes tombés par hasard sur Onsemi, mais cela s'est très bien passé, car ils ont une méthodologie de conception numérique bien au point. Il y a beaucoup de choses subtiles qui peuvent mal tourner lorsque vous concevez une puce. Mais de nos jours, les outils ont toutes sortes d'avertissements. Ils peuvent vous avertir que quelque chose ne va pas, afin que vous soyez en alerte. Il y a une grande liste de choses qui doivent être résolues pour pouvoir dire que le silicium a été compilé correctement et qu'il devrait fonctionner.

Ken : Pour en revenir au tout début du Propeller 1, Chip l’a conçu manuellement, il a fait une conception schématique. Puis nous avons commencé le Propeller 2 et nous écrivions maintenant du code Verilog. Nous avons trouvé une société extérieure pour synthétiser notre code Verilog, ciblé pour un certain processus de fonderie, mais sans fonderie spécifique à l'esprit. Cela ne se passait pas très bien. Finalement, nous nous sommes adressés directement à la fonderie qui voulait bien travailler avec nous.

Feedback de la communauté Propeller 2

Elektor : Comment avez-vous eu l'idée de donner à la communauté l'accès aux bitstreams bêta du Propeller 2 ?

Chip : Pour environ 100 $, vous pouvez acheter une très belle carte FPGA avec un FPGA assez important. Pendant le processus de conception, je produisais périodiquement, parfois même plusieurs fois par semaine, les dernières images FPGA pour six plateformes différentes. Je mettais ces fichiers à disposition pour que les clients puissent les essayer. Et j'ai toujours reçu un grand nombre de commentaires de la part de tous ceux qui avaient des idées de nouvelles instructions utiles, de modes de broches smarts utiles, toutes sortes de choses qui allaient bien au-delà de ce que j'aurais pu imaginer moi-même. Et c'était bien.

Et la raison pour laquelle nous avons pu utiliser toutes ces différentes plateformes est que l'architecture est évolutive. Pour la plus petite implémentation, nous aurions un rouage, un processeur ; pour la plus grande carte FPGA, nous pourrions en avoir 16. Je compilerais en fonction de la capacité de chacune. Certaines n'avaient que quelques broches smarts, d'autres avaient toutes les broches smarts. Mais lorsque nous nous sommes attelés à la conception physique de la puce, il est apparu que toute cette logique pour supporter 16 cogs allait nous donner seulement assez de place pour 128 Ko de mémoire principale. Et tout le monde était d'accord, les clients et moi, pour dire que huit cogs et 512 Ko de RAM principale seraient un bien meilleur équilibre.

Elektor : Comment les feedbacks ont-ils été intégrés dans le nouveau design ?

Chip : Je veux dire, il y avait des bugs vraiment complexes que les gens trouvaient et je ne suis pas sûr que j'allais les détecter à temps. Des choses à faire avec la FIFO pour l'exécution à partir de la mémoire centrale. Il y avait de vrais dormeurs là-dedans. Et nous avons eu un client qui a trouvé beaucoup de choses qui ont vraiment secoué les bugs de cela. Aussi, les gens avaient des rapports de bugs ou quelque chose qui ne fonctionnait pas. Mais aussi beaucoup d'entrées comme : Peut-on avoir quelque chose qui fait cette certaine fonction ? Je rassemblais toutes ces idées et les mettais en œuvre de la manière qui me semblait la plus efficace. Et nous avions beaucoup de personnes à bord qui avaient un bon goût dans la façon dont les choses pouvaient être arrangées pour que ce soit facile à vivre, pour que le programmeur ait un temps facile.

Elektor : Quelle était la taille de cette communauté qui s'intéressaient à la conception ?

Chip : Je pense que nous avions peut-être au moins une douzaine de personnes, peut-être plus. C'est difficile à dire. Je pense que la moitié d'entre elles étaient des contributeurs importants. Et l'autre moitié l'était aussi, mais de manière un peu plus occasionnelle. Mais avec chacune apportant leur contribution, cela a vraiment enrichi la conception.

Ken : Il y a eu des moments où Chip a vraiment eu beaucoup de difficultés. Et la communauté l'a vraiment sauvé et encouragé à continuer dans la bonne direction. Les mêmes contributeurs ont suivi et ont apporté de la documentation, du support et du code à la communauté.

Chip : Je veux dire, il a fallu tant d'années, à un moment donné mon père a dit, parce qu'il avait toujours été impliqué dans notre entreprise, « tu n'as pas à terminer cette chose, tu peux t'arrêter maitenant. » Cela faisait 10 ou 11 ans que ça durait. Et j'ai presque pensé à arrêter, mais je ne pouvais pas, parce qu'il y avait trop de choses à faire, et j'ai aimé travailler dessus de toute façon. Il a fallu beaucoup de ressources au fil du temps. Je veux dire que nous avons dépensé peut-être 6 millions de dollars sur ce projet pendant toutes ces années.

Codage

Elektor : L'utilisation de SPIN2 et d’Assembler peut être agréable, mais beaucoup d'entre nous ont l'habitude de coder également en C/C++. Allez-vous nous aider à obtenir un support C/C++ pour le Propeller 2 ?

Chip : Ce n'est pas un projet officiel de Parallax, mais nous avons une personne. Son nom est Eric Smith, et il a écrit un très bon compilateur qui est, dans certains domaines, bien plus avancé que mon propre compilateur SPIN. Il est basé sur GCC, qui fait en fait SPIN2, SPIN, C, et même BASIC. Son outil s'appelle FlexProp et il fonctionne sous Windows, Mac et Linux. Le silicium a de très bonnes possibilités de faire du pas à pas, de stopper et de regarder les choses pendant l'exécution. Mais je dois terminer cela de mon côté, et alors il sera en mesure de l'implémenter dans son outil, afin qu'il puisse faire du single step à partir du code source. Il est très réactif et corrige tout ce que l'on remarque comme étant erroné. Je dirais que son outil est assez bon, mais ce n'est pas un outil officiel de Parallax.

Elektor : De l'ensemble des outils logiciels non officiels, il y a maintenant des plugins pour le Propeller 2 ajoutés pour Visual Studio Code. Parallax supportera-t-il officiellement Visual Studio Code comme environnement de développement pour le Propeller 2 ?

Ken : Nous le supportons déjà avec l'un de nos contributeurs clés, Stephen Moraco. Et c'est là que je consacre une grande partie de mon énergie, car cela fonctionne sur Mac, Windows et Linux avec le compilateur d'Eric.

Le marché des puces

Elektor : Passons au marché des puces. Les gens ont des difficultés à obtenir du silicium. Comment cela se passe-t-il pour Parallax en ce qui concerne Onsemi et leurs capacités de production ? Est-ce que vous recevez toujours le silicium que vous avez commandé ?

Ken : Nous recevons tout ce que nous avons commandé, dans les délais habituels, mais plus cher.

Chip : Les coûts ne cessent d'augmenter de nos jours, nous devons donc nous recalibrer.

Ken : Je pense que nous n'avons pas encore vraiment trouvé le bon prix pour le Propeller 2. Un client vient de passer une commande de 250 unités et a payé environ 12 dollars chacune. Mais j'aimerais vraiment pouvoir les vendre autour de 10 $ à des volumes élevés. C'est vraiment l'objectif et il semble que nous soyons en train d'atteindre ce prix cible maintenant.

Elektor : Avez-vous déjà envisagé de passer à un processus plus avancé que le 180 nm en fonderie pour le Propeller 2 ? Afin d'obtenir plus de puces à partir d'une seule plaquette et d'être moins cher au final ?

Chip : Le problème est que les coûts se multiplient. En 180 nanomètres, le coût final était de 600 000 dollars, alors qu'il avait été estimé à 270 000 dollars au départ. Je crois que quelqu'un nous a dit que nous pouvions faire du 65 nanomètres, peut-être même quelque chose de plus grand, mais le coût était estimé à 600 000 dollars. Je me souviens de la puce que nous voulions fabriquer et qui consommait 8 W en 180 nm. Avec un processus de 40 nm, elle aurait eu besoin de 9 mW pour le même nombre de cœurs. Et elle aurait probablement été capable de cadencer jusqu'à 1,2 GHz ou 1,4 GHz. Il aurait donc été beaucoup plus petit, plus rapide et moins gourmand en énergie. Nous pourrions le faire ; il nous faudrait juste probablement un million de dollars pour passer à 40 nm.

Quelles sont les prochaines étapes ?

Elektor : Le Propeller 2 étant maintenant terminé, avez-vous commencé à penser à un Propeller 3 ?

Chip : Nous avons déjà pensé au Propeller 3. Mais ce que nous devons faire, c'est réaliser suffisamment de revenus avec Propeller 2 pour le financer. Avec un peu de chance, ce sera le cas. Le Propeller 2 fait beaucoup de choses nouvelles que les gens aimeraient avoir, mais il est en dehors du circuit où beaucoup de choses sont aujourd'hui, et c'est donc un défi d'attirer les clients.

Elektor : Vos cœurs utilisent une architecture propriétaire. RISC-V sera-t-il une option pour le prochain ?

Chip : Nous avons eu quelques clients qui ont participé aux efforts de conception FPGA pour le Propeller 2 et qui étaient intéressés par RISC-V et ils l'ont beaucoup apprécié. Je pense que le principal avantage du RISC-V est qu'il est associé à un écosystème, ce qui rendrait la communication, par exemple, d'une puce Propeller 3 avec RISC-V beaucoup plus facile pour le client que de devoir lui expliquer de nouvelles choses. Je pense que le RISC-V est une architecture assez efficace. Avec, nous pourrions être poussés vers le paradigme ARM où il faut soudainement avoir un silicium dédié pour faire quoi que ce soit en temps réel. Étant donné que les compilateurs qui préparent le code à fonctionner sur RISC-V ne vont probablement pas penser aux temps de cycle, son implémentation pourrait avoir quelques niveaux de cache, rendant le timing moins prévisible. Pour moi, ce n'est pas si intéressant, car nous devrions compenser, donc notre contribution devrait se faire en termes de broches intelligentes.

Note de l'auteur : le Propeller 2 est unique à bien des égards. Si vous souhaitez en savoir plus sur cette puce et avoir une première impression, jetez un coup d'œil à la série de Mathias Claussen, « Propeller 2 de Parallax ». Au fur et à mesure que la documentation et l'outillage du Propeller 2 s'améliorent, nous pourrions y revenir dans une autre série d'articles.

Des questions sur le Propeller 2 ?

Vous avez des questions techniques ou des commentaires sur cet article ? Envoyez un e-mail aux auteurs à mathias.claussen@elektor.com et luc.lemmens@elektor.com.

Traduction : Maxime Valens

Discussion (0 commentaire(s))