Topologie de grille enveloppante: les limites de la loi de Moore?

20 juin 2018

sur

sur

En s’associant avec Unisantis Electronics, entreprise basée à Singapour, l’institut belge de recherche Imec a développé le SGT (Surrounding Gate Transistor, ou transistor à grille enveloppante), topologie qui permet de fabriquer une cellule SRAM unique à l’aide de seulement six transistors à 5 nm.

Pour la plupart des chercheurs en semi-conducteurs, la production de structures de plus en plus miniaturisées est un objectif permanent. Ces structures approchant des dimensions atomiques, la limite physique de la loi de Moore risque d’être atteinte. Cependant, grâce à une topologie de cellule verticale dite « à grille enveloppante » (SGT), développée par Unisantis, il est possible de ramener l’encombrement d'une cellule SRAM à 6 transistors à une surface à peine comprise entre 0,0184 et 0,0205 μm2. Cette topologie permet d'obtenir une réduction de surface de 20 à 30 % par comparaison avec les transistors à structure FET horizontale enrobante. La structure verticale apporte aussi d'autres avantages, avec notamment une tension de fonctionnement, une stabilité et un courant de fuite plus performants.

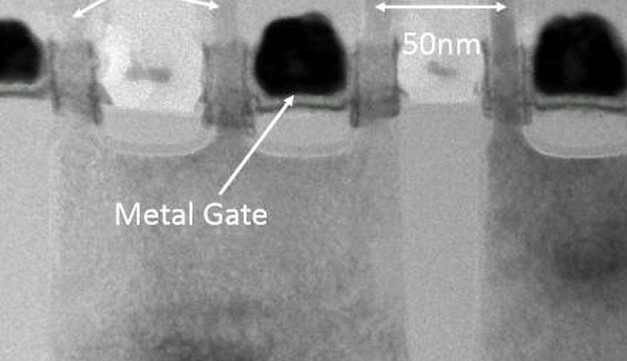

SGT (Surrounding-Gate transistor). Image avec l’aimable autorisation d’Unisantis.

L’utilisation d'une topologie « à grille enveloppante » permet une commande électrostatique quasi-parfaite du canal FET. Réalisée à l'aide de cette technique, une cellule SRAM d'une surface de 0,0205 μm2 nécessite un pas de colonnes minimal de 50 nm, ce qui permet d'obtenir un facteur d'échelle supérieur de 24 % aux cellules SRAM classiques les plus petites. Les coûts de fabrication devraient être comparables à ceux des SRAM finFET classiques à condition de pouvoir optimiser le nombre de processus en utilisant des techniques de lithographie EUV (rayonnement ultraviolet extrême) à simple exposition.

Pour la plupart des chercheurs en semi-conducteurs, la production de structures de plus en plus miniaturisées est un objectif permanent. Ces structures approchant des dimensions atomiques, la limite physique de la loi de Moore risque d’être atteinte. Cependant, grâce à une topologie de cellule verticale dite « à grille enveloppante » (SGT), développée par Unisantis, il est possible de ramener l’encombrement d'une cellule SRAM à 6 transistors à une surface à peine comprise entre 0,0184 et 0,0205 μm2. Cette topologie permet d'obtenir une réduction de surface de 20 à 30 % par comparaison avec les transistors à structure FET horizontale enrobante. La structure verticale apporte aussi d'autres avantages, avec notamment une tension de fonctionnement, une stabilité et un courant de fuite plus performants.

L’utilisation d'une topologie « à grille enveloppante » permet une commande électrostatique quasi-parfaite du canal FET. Réalisée à l'aide de cette technique, une cellule SRAM d'une surface de 0,0205 μm2 nécessite un pas de colonnes minimal de 50 nm, ce qui permet d'obtenir un facteur d'échelle supérieur de 24 % aux cellules SRAM classiques les plus petites. Les coûts de fabrication devraient être comparables à ceux des SRAM finFET classiques à condition de pouvoir optimiser le nombre de processus en utilisant des techniques de lithographie EUV (rayonnement ultraviolet extrême) à simple exposition.

Lire l'article complet

Hide full article

Discussion (0 commentaire(s))